# ECE 198JL Third Midterm Exam Fall 2013

Tuesday, November 12th, 2013

| Name:               |         | NetID:   |  |

|---------------------|---------|----------|--|

| Discussion Section: | I       | <u> </u> |  |

| 10:00 AM            | [ ] JD1 |          |  |

| 11:00 AM            | [ ] JD2 |          |  |

| 12:00 PM            | [ ] JD7 |          |  |

| 1:00 PM             | [ ] JD9 | [ ] JDA  |  |

| 2:00 PM             | [ ] JDB |          |  |

| 3:00 PM             | [ ] JDC |          |  |

| 4:00 PM             | [ ] JD8 |          |  |

|                     |         |          |  |

- Be sure your exam booklet has 11 pages.

- Be sure to write your name and lab section on the first page.

- Do not tear the exam booklet apart; you can only detach the last page.

- We have provided LC-3 instructions set at the back.

- Use backs of pages for scratch work if needed.

- This is a closed book exam. You may not use a calculator.

- You are allowed one handwritten 8.5 x 11" sheet of notes.

- Absolutely no interaction between students is allowed.

- Be sure to clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

- Don't panic, and good luck!

| Problem 1 | 10 points:  | · |

|-----------|-------------|---|

| Problem 2 | 7 points:   |   |

| Problem 3 | 14 points:  |   |

| Problem 4 | 11 points:  |   |

| Problem 5 | 12 points:  |   |

| Problem 6 | 22 points:  |   |

| Problem 7 | 8 points:   |   |

| Problem 8 | 16 points:  |   |

|           |             |   |

| Total     | 100 points: |   |

### Problem 1 (10 pts): Sequential circuit analysis

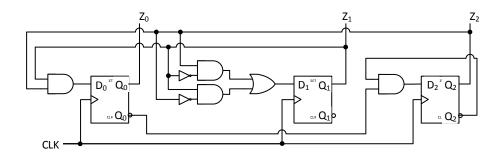

Consider the sequential circuit shown below that has three internal state bits,  $Q_2Q_1Q_0$ , and three external outputs,  $Z_2Z_1Z_0$ , that match the internal state bits, that is,  $Z_i = Q_i$ .

1. Write the flip-flop excitation equations for the  $D_2$ ,  $D_1$ , and  $D_0$  flip-flops as functions of the current state  $Q_2Q_1Q_0$ :

$$D_{2} = \overline{Q_{2}} \overline{Q_{0}} \qquad D_{1} = \underline{Q_{2}} \overline{Q_{1}} + \overline{Q_{2}} \overline{Q_{1}} \qquad D_{0} = \underline{Q_{2}} \overline{Q_{1}}$$

$$(Observe: D_{1} = Q_{2} \oplus Q_{1})$$

2. Complete the next-state table

| Cı    | urrent sta | ite   | Next state |         |         |  |  |  |

|-------|------------|-------|------------|---------|---------|--|--|--|

| $Q_2$ | $Q_1$      | $Q_0$ | $Q_2^+$    | $Q_1^+$ | $Q_0^+$ |  |  |  |

| 0     | 0          | 0     | l          | O       | 0       |  |  |  |

| 0     | 0          | 1     | 0          | 0       | 0       |  |  |  |

| 0     | 1          | 0     | l          | (       | 0       |  |  |  |

| 0     | 1          | 1     | 0          | 1       | 0       |  |  |  |

| 1     | 0          | 0     | 0          | 1       | 0       |  |  |  |

| 1     | 0          | 1     | 0          | I       | 0       |  |  |  |

| 1     | 1          | 0     | 0          | 0       | 1       |  |  |  |

| 1     | 1          | 1     | 0          | 0       | ĺ       |  |  |  |

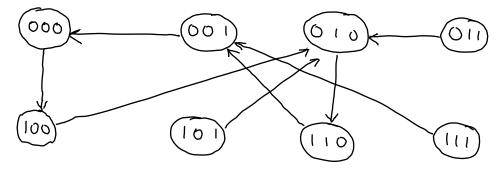

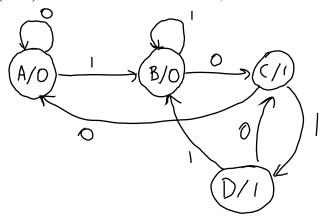

**3.** Draw the state transition diagram for this FSM.

**4.** Explain the function of this FSM in one sentence.

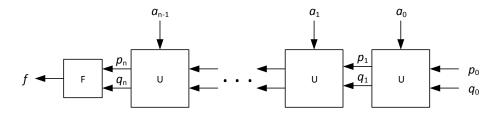

## Problem 2 (7 pts): Serial design

On Midterm 2 you designed a bit-slice circuit that checks whether an unsigned integer  $A=a_{n-1}a_{n-2}..a_1a_0$  is a power of 2, starting with the least significant bit:

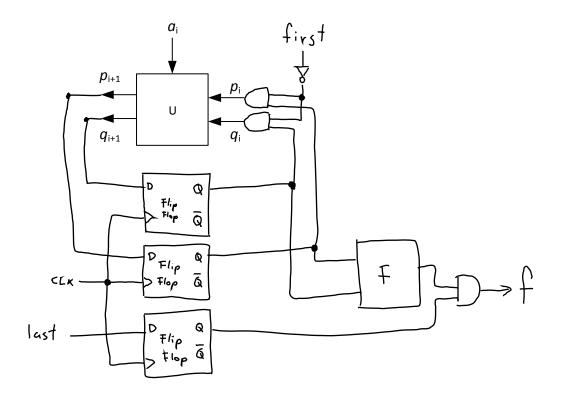

**1.** How many flip-flops are needed to construct a *serial* power-of-two checker circuit using a Moore machine model and using circuit U as is?

Answer:  $\sqrt{\omega_0}$

**2.** Re-draw the bit-sliced design shown above as a serial design using a Moore machine model. Besides adding storage elements, you also need to add a circuit that resets  $p_iq_i$  inputs to 00 when i=0 and a circuit that outputs f when i=n-1, or 0 otherwise. You can assume that two additional input signals are supplied: first=1 iff i=0 and last=1 iff i=n-1. You can also use circuit F from the above implementation as a black box.

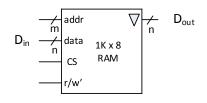

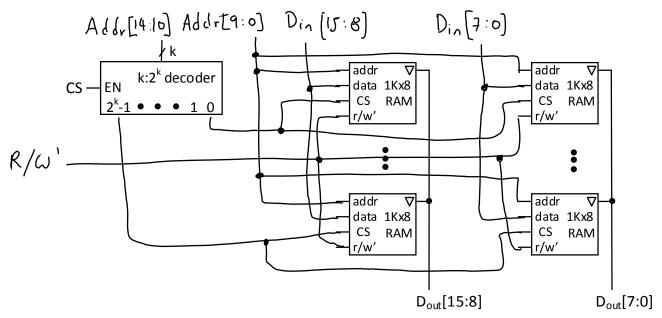

### Problem 3 (14 pts): RAM

Shown to the right is a 1K x 8 RAM.  $(1K = 2^{10})$ .

1. How many bits do the addr, data, CS, and r/w' ports require?

2. Using 1K x 8 RAM chips, implement a 32K x 16 RAM. Each 1K x 8 RAM chip has inputs data, addr, CS, and r/w' and an output gated by a tri-state buffer. Finish the implementation by drawing the missing connections and labeling all newly added wires. (You do not need to draw all the rows, they are shown as " ... ", but be sure the pattern is clear.) The RAM output wires and CS are already drawn for you.

3. How many rows of 1K x 8 RAM chips are needed and what is the value of k?

Number of rows:  $2^s = 32$  k = 5

**4.** Suppose you wish to store the decimal value -1 in memory at the address 1024. In which row (indexing from 0) of 1K x 8 RAM chip(s) will this value be stored?

Answer:  $\frac{\text{Row}}{\text{Note the address 10240 NV to discrete the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the second of the address 10240 NV to discrete the address 10240 NV to discrete the second of the address 10240 NV to discrete the$

5. What input values must be provided to your 32K x 16 RAM in order to properly store this value at the address 1024? Write the addr and data values for your 32K x 16 RAM in <a href="hexadecimal">hexadecimal</a>.

addr:  $\times$  0 4 0 0 data:  $\times$  FF FF

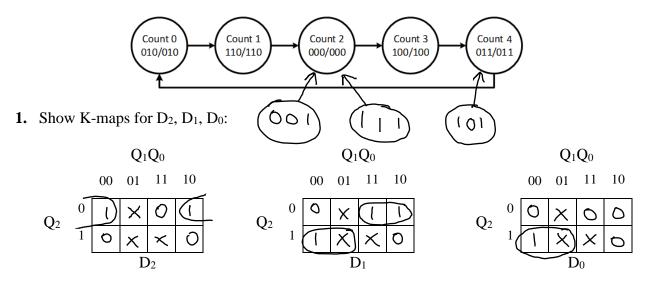

### Problem 4 (11 pts): Counter design

Using conventional sequential circuit design techniques, implement a 3-bit synchronous counter with negative-edge triggered D flip-flops that counts in the following  $Q_2Q_1Q_0$  sequence:

**2.** Write Boolean expressions for  $D_2$ ,  $D_1$ ,  $D_0$  in min SOP form:

$$D_{2} = \overline{Q_{2}} \overline{Q_{0}}$$

$$D_{1} = \overline{Q_{2}} \overline{Q_{1}} + \overline{Q_{2}} \overline{Q_{1}}$$

$$D_{0} = \overline{Q_{2}} \overline{Q_{1}}$$

$$(= Q_{1} \oplus Q_{1})$$

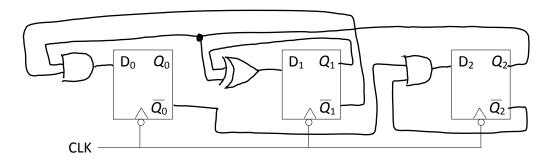

3. Draw the circuit using as few additional gates as possible.

**4.** Is your counter *self-starting*? Explain - and be specific to *your solution*. (Self-starting means that no matter in what state the counter starts, it always converges to produce the correct counting sequence.)

### Problem 5 (12 pts): Sequence recognizer design

Design a sequence recognizing FSM with input x and output z such that the output is 1 if and only if pattern 10 or 101 has been detected in the input stream. Make sure to detect overlapping patterns.

Example:

| Input:  | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Output: | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

1. Draw the <u>Moore</u> state diagram, using as few states as possible. (Solutions with more than 5 states are not acceptable.) Let A be the start state. Each edge must be labeled with x and each node (state) must be labeled with *name*/z.

**2.** Write down your *state meanings*, e.g., "A – start state":

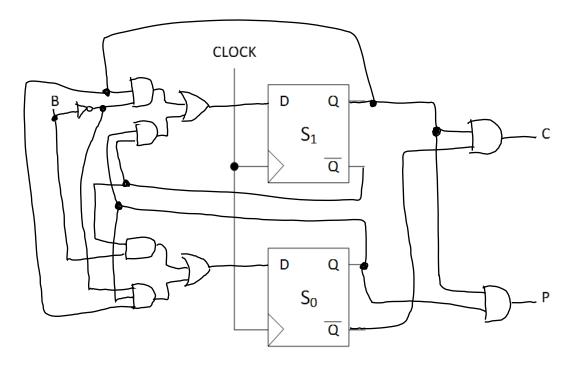

### Problem 6 (22 pts): Bluetooth headset FSM

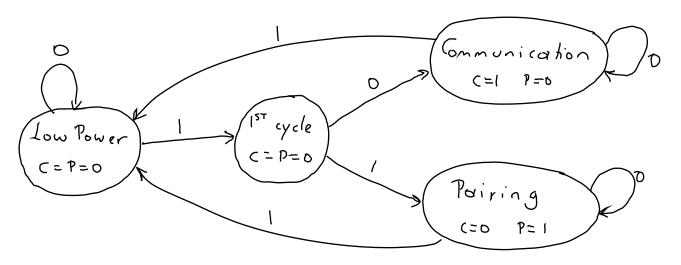

A wireless Bluetooth headset for a cell phone has one button (B=1, when pressed) to control all of its functionality. When the device is "off," the system is in a low power state waiting for the user to turn it on. If the headset is "off" and the user presses the system button for one cycle, the headset will turn "on" and tell the cell phone that it is ready for communication by setting signal C=1. If the headset is "off" and the user presses the system button for two cycles, the headset will turn on into "pairing" mode and broadcast a pairing signal by setting P=1. If the user presses the system button while it is on or in pairing mode, then the headset will turn off. Note: Each part will be graded based on your previous section, so if you cannot perfectly solve part 1, finish the other sections based on whatever solution you find for Part 1.

1. Design a Moore FSM implementing this system. Give your states meaningful names so that we can comprehend your design intent. Sketch the complete state transition diagram for your FSM, specifying input *B* for each transition and outputs *C* and *P* for each state. (You do not need more than 4 states or a counter. Carefully consider how you will count the cycles that the button is pressed.)

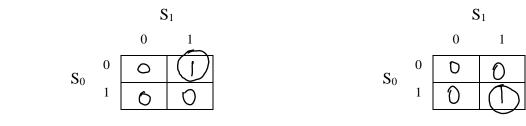

**2.** Fill in the truth table below by assigning internal state bit representations  $S_1S_0$  and output values C and P for each of your states from Part 1 and then filling in the values for the next-state variables  $S_1^+$  and  $S_0^+$  for each combination of  $S_1S_0B$ . This part will be graded based on your FSM in part 1.

|                        | Cur   | rent  | External | Next    | State   | Exte     | rnal   |  |

|------------------------|-------|-------|----------|---------|---------|----------|--------|--|

| State name and meaning | sta   | ate   | Input B  |         |         | Out      | puts   |  |

| _                      | $S_1$ | $S_0$ | В        | $S_1^+$ | $S_0^+$ | C        | P      |  |

| ) 7                    |       | 10    | 0        | 0       | 0       | $\cap$   | $\sim$ |  |

| Low Power              | 0     | 0     | 1        | 0       | l       | )        |        |  |

| 15T cycle              |       | ı     | 0        | l       | 0       | $\wedge$ | Λ      |  |

| 1, 64616               |       | I     | 1        | l       | 1       | )        |        |  |

|                        | 1     | (     | 0        | l       | 9       | 1        | 7      |  |

| Communication          | (     |       | 1        | O       | O       | l        |        |  |

| During                 | ١     | 1     | 0        | 1       | 1       | $\cap$   |        |  |

| Pairing                | \     |       | 1        | 0       | 0       | )        | ı      |  |

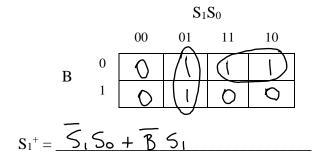

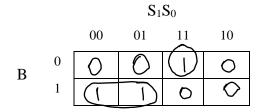

**3.** Using the next state table that you wrote in Part 2, fill in the K-maps for  $S_I^+$ ,  $S_0^+$ , C, and P and derive **minimal SOP** Boolean expressions for these variables.

$$S_0^+ = \overline{BS_1} + \overline{BS_1S_0}$$

**4.** Add gates as necessary to complete the implementation of your FSM using the two positive edge-triggered D flip-flops shown below.

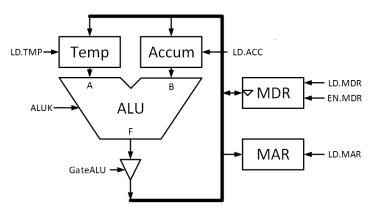

### Problem 7 (8 pts): Register transfer

Digital Signal Processing units, like those found in your cell phone, are specialized architectures that use an Accumulator register (Accum) to store the results of all arithmetic operations. The architecture also has a Temporary register (Temp) to store a second operand. The ALU, Memory Data Register (MDR), and Memory Address Register (MAR) are used for the same purpose as in the LC-3. The ALU function table is shown below. The ALU and MDR can both send data to the system bus but only as allowed by the GateALU and EN.MDR signals, respectively. When EN.MDR is 1, MDR's content is output on the bus. When LD.MDR is 1, MDR stores value from the bus. When GateALU is 1, ALU's output is connected to the bus.

| ALUK | Operation           | Explanation |

|------|---------------------|-------------|

| 00   | Pass A              | F = A       |

| 01   | Pass B              | F = B       |

| 10   | Clear               | F = 0       |

| 11   | Multiply-Accumulate | F = A*B + B |

- 1. The Accumulator is part of the <u>Processing</u> unit of a von Neumann architecture.

- **2.** Assign values to the control signals to execute the following RTL instructions. If the RTL instruction cannot be implemented, write "IMPOSSIBLE." For the last row, determine what RTL instruction is implemented by the selected control signals.

|                              | CONTROL SIGNALS |         |        |        |        |         |               |                 |            |

|------------------------------|-----------------|---------|--------|--------|--------|---------|---------------|-----------------|------------|

| RTL Instruction              | TMP (1          | LD. IMI | LD.ACC | LD.MDR | LD.MAR | GateALU | EN.MDR        | ALUK            |            |

| MAR ← Accum                  | (               | Ò       | 0      | ٥      | 1      | 1       | 0             | 61              |            |

| Accum ← Temp * Accum + Accum |                 | )       | 1      | 0      | 0      | (       | $\mathcal{C}$ | 11              | •          |

| Accum ← MAR                  | ,               |         |        |        |        |         |               | ~               | Impossible |

| Temp ← MDR                   | (               |         | 0      | 0      | 0      | 0       | )             | $\times \times$ | •          |

| MOR CO                       | C               | )       | 0      | 1      | 0      | 1       | 0             | 10              |            |

9

### Problem 8 (16 pts): LC-3 ISA

The following LC-3 program fragment, represented as three hexadecimal numbers, is stored in memory at the indicated locations and the following values are stored in registers:

| address | instruction |

|---------|-------------|

|         |             |

| xC100   | xA801       |

| xC101   | x1322       |

| xC102   | xC100       |

|         |             |

|         | value             | register |  |  |  |

|---------|-------------------|----------|--|--|--|

|         | x4005             | R0       |  |  |  |

| x A803  | ×4004             | R1       |  |  |  |

|         | x4003             | R2       |  |  |  |

|         | x4002             | R3       |  |  |  |

| X A 801 | <del>-x4001</del> | R4       |  |  |  |

**1.** Re-write three instructions in binary representation and provide their corresponding RTL. (*Note: formats of the entire LC-3 instruction set are provided at the end of the exam booklet.*)

| address | instruction | binary instruction  | RTL (be specific to this |

|---------|-------------|---------------------|--------------------------|

|         |             |                     | instruction)             |

| xC100   | xA801       | 1010 1000 0000 0001 | R4-M[M[xC102]]           |

| xC101   | x1322       | 0001 0011 0010 0610 | R1 ← R4+2                |

| xC102   | xC100       | 0000 0000 0000      | PC R4                    |

2. Assuming PC is initially set to xC100, trace the execution of the given program segment for three instruction cycles, filling in the table below. Write down the values stored in the PC, IR, MAR, MDR, N, Z, and P registers at the end of each instruction cycle. Values for PC, IR, MAR, and MDR should be written in hexadecimal. Values for N, Z, and P should be written in binary.

| PC      | IR     | MAR    | MDR      | N | Z | P |

|---------|--------|--------|----------|---|---|---|

| x < 101 | × A801 | x C100 | X A801   | 1 | 0 | 0 |

| XCIOZ   | ×1322  | XClol  | x 1322   | ( | 0 | 0 |

| XYBOI   | × C100 | x Cloz | x C ( 00 | 1 | O | 0 |

3. What hexadecimal value will be stored in R1 after the three instruction cycles?

Answer: × A 803

**4.** What is the address of the next instruction to be executed after the three instruction cycles?

Answer: × A 801

**5.** How many memory reads will take place during these three instruction cycles, including the instruction FETCH?

# NOTES: RTL corresponds to execution (after fetch!); JSRR not shown

| $R7 \leftarrow PC$ , $PC \leftarrow M[ZEXT(trapvect8)]$ | TRAP 1111 0000 trapvect8 TRAP                | R7 ← PC, PC ← PC + SEXT(PCoffset11) | JSR 0100 1 PCoffset11 JSR PG        | PC ← BaseR                   | JMP 1100 000 BaseR 000000 JMP BaseR | ((n AND N) OR (z AND Z) OR (p AND P)):<br>PC ← PC + SEXT(PCoffset9) | BR 0000 n z p PCoffset9 BR{nzp | DR ← SR1 AND SEXT(imm5), Setcc   | AND 0101 DR SR1 1 imm5 AND D        | DR ← SR1 AND SR2, Setcc              | AND 0101 DR SR1 0 00 SR2 AND D               | DR ← SR1 + SEXT(imm5), Setcc           | ADD 0001 DR SR1 1 imm5 ADD DF       | DR ← SR1 + SR2, Setcc               | ADD 0001 DR SR1 0 00 SR2 ADD DF    |

|---------------------------------------------------------|----------------------------------------------|-------------------------------------|-------------------------------------|------------------------------|-------------------------------------|---------------------------------------------------------------------|--------------------------------|----------------------------------|-------------------------------------|--------------------------------------|----------------------------------------------|----------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|

|                                                         | TRAP trapvect8 STR                           |                                     | JSR PCoffset11 STI                  |                              | aseR ST                             |                                                                     | BR{nzp} PCoffset9 NOT          |                                  | AND DR, SR1, imm5 LEA               |                                      | AND DR, SR1, SR2 LDR                         |                                        | ADD DR, SR1, imm5 LDI               |                                     | ADD DR, SR1, SR2 LD                |

| M[BaseR + SEXT(offset6)] ← SR                           | 0111 SR BaseR offset6 STR SR, BaseR, offset6 | M[M[PC + SEXT(PCoffset9)]] ← SR     | 1011 SR PCoffset9 STI SR, PCoffset9 | M[PC + SEXT(PCoffset9)] ← SR | 0011 SR PCoffset9 ST SR, PCoffset9  | DR ← NOT SR, Setcc                                                  | 1001 DR SR 1111111 NOT DR, SR  | DR ← PC + SEXT(PCoffset9), Setcc | 1110 DR PCoffset9 LEA DR, PCoffset9 | DR ← M[BaseR + SEXT(offset6)], Setcc | 0110 DR BaseR offset6 LDR DR, BaseR, offset6 | DR ← M[M[PC + SEXT(PCoffset9)]], Setcc | 1010 DR PCoffset9 LDI DR, PCoffset9 | DR ← M[PC + SEXT(PCoffset9)], Setcc | 0010 DR PCoffset9 LD DR, PCoffset9 |